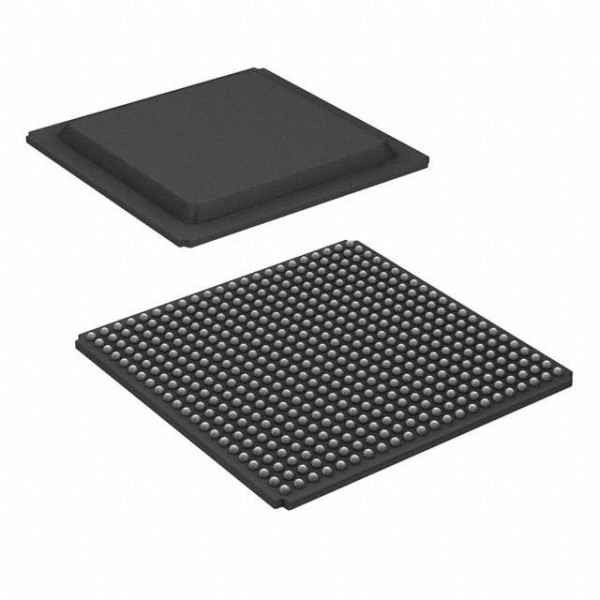

Matriz de portas programáveis em campo XC6SLX75-2FGG484C

♠ Descrição do produto

| Atributo do produto | Valor do Atributo |

| Fabricante: | Xilinx |

| Categoria do produto: | FPGA - Matriz de Portas Programáveis em Campo |

| RoHS: | Detalhes |

| Série: | XC6SLX75 |

| Número de Elementos Lógicos: | 74637 LE |

| Número de E/Ss: | 280 E/S |

| Tensão de alimentação - Mín.: | 1,14 V |

| Tensão de alimentação - Máx.: | 1,26 V |

| Temperatura mínima de operação: | 0 C |

| Temperatura máxima de operação: | + 85 °C |

| Taxa de dados: | - |

| Número de transceptores: | - |

| Estilo de montagem: | SMD/SMT |

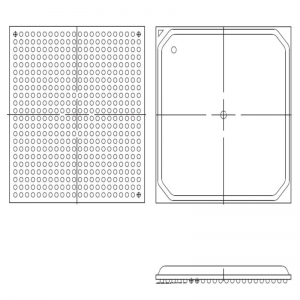

| Pacote/Caixa: | FCBGA-484 |

| Marca: | Xilinx |

| RAM distribuída: | 692 kbit |

| RAM de bloco embarcada - EBR: | 3096 kbit |

| Frequência máxima de operação: | 1080 MHz |

| Sensível à umidade: | Sim |

| Número de blocos de matriz lógica - LABs: | 5831 LAB |

| Tensão de alimentação operacional: | 1,2 V |

| Tipo de produto: | FPGA - Matriz de Portas Programáveis em Campo |

| Quantidade de embalagem de fábrica: | 1 |

| Subcategoria: | CIs de lógica programável |

| Nome comercial: | espartano |

| Peso unitário: | 1,662748 onças |

♠ Visão geral da família Spartan-6

A família Spartan®-6 oferece recursos de integração de sistemas de ponta com o menor custo total para aplicações de alto volume. A família de treze membros oferece densidades expandidas que variam de 3.840 a 147.443 células lógicas, com metade do consumo de energia das famílias Spartan anteriores, além de conectividade mais rápida e abrangente. Construída com base em uma tecnologia de processo de cobre de baixo consumo de 45 nm, que proporciona o equilíbrio ideal entre custo, potência e desempenho, a família Spartan-6 oferece uma nova lógica de tabela de consulta (LUT) de 6 entradas e registro duplo, mais eficiente, e uma rica seleção de blocos integrados em nível de sistema. Isso inclui RAMs de bloco de 18 Kb (2 x 9 Kb), fatias DSP48A1 de segunda geração, controladores de memória SDRAM, blocos aprimorados de gerenciamento de clock de modo misto, tecnologia SelectIO™, blocos transceptores seriais de alta velocidade otimizados para energia, blocos de endpoint compatíveis com PCI Express®, modos avançados de gerenciamento de energia em nível de sistema, opções de configuração de detecção automática e segurança IP aprimorada com proteção AES e Device DNA.

Esses recursos oferecem uma alternativa programável de baixo custo a produtos ASIC personalizados, com facilidade de uso sem precedentes. Os FPGAs Spartan-6 oferecem a melhor solução para projetos lógicos de alto volume, projetos de DSP voltados para o consumidor e aplicações embarcadas com custo-benefício. Os FPGAs Spartan-6 são a base programável de silício para Plataformas de Design Direcionado, que fornecem componentes integrados de software e hardware que permitem que os projetistas se concentrem na inovação desde o início do ciclo de desenvolvimento.

• Família Spartan-6:

- Spartan-6 LX FPGA: Lógica otimizada

- Spartan-6 LXT FPGA: Conectividade serial de alta velocidade

• Projetado para baixo custo

- Vários blocos integrados eficientes

- Seleção otimizada de padrões de E/S

- Almofadas escalonadas

- Embalagens de plástico de alto volume com fios soldados

• Baixa potência estática e dinâmica

- Processo de 45 nm otimizado para custo e baixo consumo de energia

- Modo de hibernação para energia zero

- O modo de suspensão mantém o estado e a configuração com ativação de vários pinos e aprimoramento de controle

- Tensão de núcleo de 1,0 V de baixa potência (FPGAs LX, apenas -1L)

- Tensão de núcleo de 1,2 V de alto desempenho (FPGAs LX e LXT, graus de velocidade -2, -3 e -3N)

• Bancos de interface SelectIO™ multivoltagem e multipadrão

- Taxa de transferência de dados de até 1.080 Mb/s por E/S diferencial

- Saída de acionamento selecionável, até 24 mA por pino

- Padrões e protocolos de 3,3 V a 1,2 VI/O

- Interfaces de memória HSTL e SSTL de baixo custo

- Conformidade com hot swap

- Taxas de variação de E/S ajustáveis para melhorar a integridade do sinal

• Transceptores seriais GTP de alta velocidade nos FPGAs LXT

- Até 3,2 Gb/s

- Interfaces de alta velocidade, incluindo: Serial ATA, Aurora, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort e XAUI

• Bloco de endpoint integrado para projetos PCI Express (LXT)

• Suporte à tecnologia PCI® de baixo custo compatível com as especificações de 33 MHz, 32 e 64 bits.

• Fatias DSP48A1 eficientes

- Aritmética de alto desempenho e processamento de sinais

- Multiplicador rápido de 18 x 18 e acumulador de 48 bits

- Capacidade de pipeline e cascata

- Pré-somador para auxiliar aplicações de filtros

• Blocos de controlador de memória integrados

- Suporte a DDR, DDR2, DDR3 e LPDDR

- Taxas de dados de até 800 Mb/s (largura de banda máxima de 12,8 Gb/s)

- Estrutura de barramento multiporta com FIFO independente para reduzir problemas de tempo de projeto

• Recursos lógicos abundantes com capacidade lógica aumentada

- Suporte opcional para registrador de deslocamento ou RAM distribuída

- LUTs eficientes de 6 entradas melhoram o desempenho e minimizam a potência

- LUT com flip-flops duplos para aplicações centradas em pipeline

• Bloqueia RAM com uma ampla gama de granularidade

- RAM de bloco rápido com habilitação de gravação de bytes

- Blocos de 18 Kb que podem ser programados opcionalmente como duas RAMs de bloco de 9 Kb independentes

• Clock Management Tile (CMT) para melhor desempenho

- Baixo ruído, clocking flexível

- Os gerenciadores de relógio digital (DCMs) eliminam a distorção do relógio e do ciclo de trabalho

- Loops de bloqueio de fase (PLLs) para clock de baixo jitter

- Síntese de frequência com multiplicação, divisão e deslocamento de fase simultâneos

- Dezasseis redes de relógios globais de baixa assimetria

• Configuração simplificada, suporta padrões de baixo custo

- Configuração de detecção automática de 2 pinos

- Amplo suporte a SPI de terceiros (até x4) e flash NOR

- Plataforma Xilinx Flash rica em recursos com JTAG

- Suporte MultiBoot para atualização remota com vários fluxos de bits, usando proteção watchdog

• Segurança aprimorada para proteção de design

- Identificador de DNA de dispositivo exclusivo para autenticação de design

- Criptografia de fluxo de bits AES em dispositivos maiores

• Processamento embarcado mais rápido com processador MicroBlaze™ aprimorado e de baixo custo

• Projetos de referência e IP líderes do setor