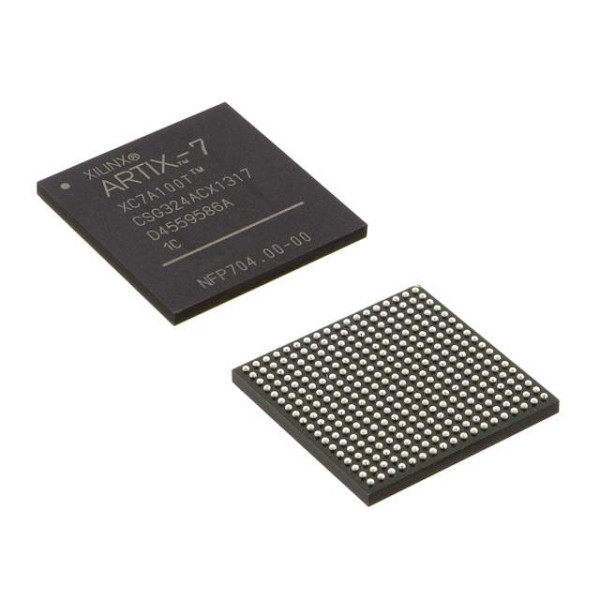

XC7A50T-2CSG324I FPGA – Matriz de portas programáveis em campo XC7A50T-2CSG324I

♠ Descrição do produto

| Atributo do produto | Valor do Atributo |

| Fabricante: | Xilinx |

| Categoria do produto: | FPGA - Matriz de Portas Programáveis em Campo |

| Série: | XC7A50T |

| Número de Elementos Lógicos: | 52160 LE |

| Número de E/Ss: | 210 E/S |

| Tensão de alimentação - Mín.: | 0,95 V |

| Tensão de alimentação - Máx.: | 1,05 V |

| Temperatura mínima de operação: | - 40°C |

| Temperatura máxima de operação: | + 100 °C |

| Taxa de dados: | - |

| Número de transceptores: | - |

| Estilo de montagem: | SMD/SMT |

| Pacote/Caixa: | CSBGA-324 |

| Marca: | Xilinx |

| RAM distribuída: | 600 kbit |

| RAM de bloco embarcada - EBR: | 2700 kbit |

| Sensível à umidade: | Sim |

| Número de blocos de matriz lógica - LABs: | 4075 LAB |

| Tensão de alimentação operacional: | 1 V |

| Tipo de produto: | FPGA - Matriz de Portas Programáveis em Campo |

| Quantidade de embalagem de fábrica: | 1 |

| Subcategoria: | CIs de lógica programável |

| Nome comercial: | Artix |

| Peso unitário: | 1 onça |

♠ Os FPGAs da série Xilinx® 7 abrangem quatro famílias de FPGAs que atendem a toda a gama de requisitos do sistema, desde baixo custo, pequeno fator de forma, aplicações de alto volume e sensíveis ao custo até largura de banda de conectividade de ponta, capacidade lógica e capacidade de processamento de sinal para as aplicações de alto desempenho mais exigentes

Os FPGAs Xilinx® série 7 abrangem quatro famílias de FPGAs que atendem a uma gama completa de requisitos de sistema, desde aplicações de alto volume, baixo custo e pequeno formato, sensíveis ao custo, até largura de banda de conectividade ultra-alta, capacidade lógica e capacidade de processamento de sinais para as aplicações de alto desempenho mais exigentes. Os FPGAs da série 7 incluem:

• Família Spartan®-7: Otimizada para baixo custo, menor consumo de energia e alto desempenho de E/S. Disponível em um formato compacto e de baixo custo para o menor tamanho de PCB.

• Família Artix®-7: Otimizada para aplicações de baixo consumo que exigem transceptores seriais e alta taxa de transferência lógica e DSP. Oferece o menor custo total de materiais para aplicações de alta taxa de transferência e com custo reduzido.

• Família Kintex®-7: otimizada para melhor custo-benefício com uma melhoria de 2X em comparação à geração anterior, possibilitando uma nova classe de FPGAs.

• Família Virtex®-7: Otimizada para o mais alto desempenho e capacidade do sistema, com uma melhoria de 2X no desempenho do sistema. Dispositivos de altíssima capacidade habilitados pela tecnologia de interconexão de silício empilhado (SSI).

Construídos com base em uma tecnologia de processo de última geração, de alto desempenho, baixo consumo de energia (HPL), 28 nm, high-k metal gate (HKMG), os FPGAs da série 7 permitem um aumento incomparável no desempenho do sistema com 2,9 Tb/s de largura de banda de E/S, capacidade de 2 milhões de células lógicas e DSP de 5,3 TMAC/s, consumindo 50% menos energia do que os dispositivos da geração anterior para oferecer uma alternativa totalmente programável aos ASSPs e ASICs.

• Lógica FPGA avançada de alto desempenho baseada em tecnologia de tabela de consulta (LUT) de 6 entradas reais, configurável como memória distribuída.

• Bloco de RAM de porta dupla de 36 Kb com lógica FIFO integrada para buffer de dados no chip.

• Tecnologia SelectIO™ de alto desempenho com suporte para interfaces DDR3 de até 1.866 Mb/s.

• Conectividade serial de alta velocidade com transceptores multi-gigabit integrados de 600 Mb/s a taxas máximas de 6,6 Gb/s até 28,05 Gb/s, oferecendo um modo especial de baixo consumo de energia, otimizado para interfaces chip a chip.

• Uma interface analógica configurável pelo usuário (XADC), incorporando conversores analógico-digitais duplos de 12 bits 1MSPS com sensores térmicos e de alimentação no chip.

• Fatias DSP com multiplicador de 25 x 18, acumulador de 48 bits e pré-somador para filtragem de alto desempenho, incluindo filtragem de coeficiente simétrico otimizada.

• Blocos poderosos de gerenciamento de clock (CMT), combinando blocos de loop de bloqueio de fase (PLL) e gerenciador de clock de modo misto (MMCM) para alta precisão e baixa instabilidade.

• Implante rapidamente o processamento incorporado com o processador MicroBlaze™.

• Bloco integrado para PCI Express® (PCIe), para designs de Endpoint e Root Port de até x8 Gen3.

• Ampla variedade de opções de configuração, incluindo suporte para memórias comuns, criptografia AES de 256 bits com autenticação HMAC/SHA-256 e detecção e correção de SEU integradas.

• Chip flip-chip bare-die de baixo custo, wire-bond e encapsulamento flip-chip de alta integridade de sinal, oferecendo fácil migração entre membros da família no mesmo pacote. Todos os pacotes disponíveis sem chumbo e pacotes selecionados com a opção de chumbo.

• Projetado para alto desempenho e menor consumo de energia com 28 nm, HKMG, processo HPL, tecnologia de processo de tensão de núcleo de 1,0 V e opção de tensão de núcleo de 0,9 V para consumo de energia ainda menor.